# 13<sup>th</sup> IEEE International New Circuits And Systems Conference (NEWCAS 2015)

June 7-10, 2015

Minatec, Parvis Louis Néel, 38054 Grenoble, France.

http://www.newcas2015.org

# Table of contents

| Welcome to NEWCAS 2015                                | 5  |

|-------------------------------------------------------|----|

| Conference Committee                                  | 7  |

| Track Chairs                                          | 8  |

| Program at a glance                                   | 10 |

| Tutorials                                             | 13 |

| Keynotes speakers                                     | 22 |

| Special Sessions                                      | 25 |

| Panel Session                                         | 31 |

| General information                                   | 32 |

| Special events of this conference                     | 33 |

| Outdoor activity "Acrobastille" / Welcome reception   | 34 |

| Coktail / Museum visit                                | 35 |

| Gala Dinner                                           | 36 |

| Technical program                                     | 37 |

| 14 <sup>th</sup> IEEE International NEWCAS Conference | 67 |

| June 26 to 29, 2016                                   | 67 |

| Vancouver BC Canada                                   | 67 |

# General and Technical Program Chairs

Dominique Morche General co-Chair

Mohamad Sawan General co-Chair

Yannis Le Guennec

Sylvain Bourdel Technical Program co-Chair Technical Program co-Chair Technical Program co-Chair

Shahriar Mirabbasi

### Welcome to NEWCAS 2015

On behalf of the organizing committee, we are very pleased to welcome you to the 13<sup>th</sup> edition of the IEEE International NEWCAS Conference.

This edition is organized by both CEA-LETI, IMEP-LAHC and TIMA from 7th to 10th of June 2015 in Grenoble. The Conference venue is located at Minatec close to the city center, at the heart of the French Silicon Valley. You will have the opportunity to interact with experts of your domains from all continents and relax while being in the Capital of the Alps. We are confident that your stay will be unforgettable. This year, a total of 326 submissions originating from 52 countries were received.

These were classified thanks to 1100 reviews. This review was carried out efficiently in a short time; we would like to warmly thank all the reviewers.

After a rigorous selection, which guarantees the high level of our conference, 133 regular contributions were scheduled in regular sessions, plus 14 other contributions in 3 special sessions. They were divided in 22 lecture sessions and 2 poster sessions. The acceptance rate for the conference is 41%. After the conference a journal special issue will be published by Springer in the "Analog Integrated Circuits and Signal Processing" International Journal. The best papers will be extended and selected to appear in this journal. NEWCAS'2015 would not exist without the work of many people. We would like to thank the organizing committee, the Technical Program Committee, the Special Sessions organizers, the Tutorials and Keynote speakers, the reviewers and finally the authors who came to present their work at this NEWCAS edition. We also wish to thank the numerous volunteers that helped the organization, especially the graduate students of CEA-LETI and IMEP-LAHC. We would like also to thank "La Mairie de Grenoble", IMEP-LAHC, TIMA and CEA-LETI for their help. Enjoy NEWCAS'2015 conference and your stay in Grenoble.

Dominique Morche and Mohamad Sawan General co-Chairs

### Conference Committee

### General Co-chairs

Dominique Morche, CEA-Leti Mohamad Sawan, Polytechnique Montréal

### Technical Program Co-chairs

Yannis Le Guennec, Univ. Grenoble Alpes, IMEP-LAHC Sylvain Bourdel, Univ. Grenoble Alpes, IMEP-LAHC Shahriar Mirabbasi, Univ. of British Columbia

### Tutorial Co-chairs

Emmanuel Pistono, Univ. Grenoble Alpes, IMEP-LAHC Hervé Barthélémy, Univ. Sud Toulon, IM2NP Gilles Jacquemod, Polytech'Nice-Sophia Roni Khazaka, Univ. Mc Gill

### Special Session Co-chairs

Gilles Sicard, CEA-Leti

Patricia Desgreys, Telecom ParisTech

Ahmed Lakhssasi, Quebec University

Nathalie Deltimple, Univ. Bordeaux I, IMS

### Finance Chair

Anne Laure Fourneret-Itie, Univ. Grenoble Alpes, TIMA

### Local Arrangement Co-chairs

Arnaud Pezeirat, CEA-Leti Ghislaine Maury, Univ. Grenoble Alpes, IMEP-LAHC

### Publication Co-chairs

Estelle Laura-Larroze, Univ. Grenoble Alpes, IMEP-LAHC Jean-Daniel Arnould, Univ. Grenoble Alpes, IMEP-LAHC Thomas Ea, ISEP

### Publicity Co-chairs

Rodrigo Possamai Bastos, Univ. Grenoble Alpes, TIMA Ricardo Reis, UFRGS, Brazil Zhihua Wang, Tsinghua University Magdy Bayoumi, Univ. of Louisiana

### **Industry Liaison**

Peter Stokes, CMC, Canada Marc Belleville, CEA-Leti

#### IEEE Liaison

Laurent Fesquet, Univ. Grenoble Alpes, TIMA Tan Phu Vuong, Univ. Grenoble Alpes, IMEP-LAHC

### Track Chairs

### Track 1: Analog Circuits & Systems Design

Wenceslas Rahajandraibe, IM2NP, Université d'Aix-Marseille, France Salvatore Pennisi, DIEEI, University of Catania, Italy Danilo Demarchi, Politecnico di Torino, Italy Günhan Dündar, Boğaziçi University, Turkey Vincent Frick, Université de Strasbourg, France

### Track 2: Biomedical Circuits & Systems

Benoit Gosselin, Université Laval, Canada Noëlle Lewis, IMS, Université de Bordeaux, France Edith Kussener, IM2NP, ISEN Toulon, France

### Track 3: Digital circuit design and Low Power

Massimo Alioto, ECE department of the National University of Singapore Olivier Sentieys, INRIA, Université de Rennes, France Edith Beigné, CEA-Leti, France Pasquale Corsonello, University of Calabria, Italy

### Track 4: Mixed Signal Circuits & Data Converters

Glenn Cowan, Concordia University, Canada He Tang, University of Electronic Science and Technology of China Erkan Isa, Fraunhofer-Gesellschaft, Germany Marcello de Matteis, University of Milan Bicocca, Italy

### Track 5: Test and Verification

Patrick Girard, CNRS, LIRMM, France Lirida Naviner, Telecom Paritech, France

### Track 6: Digital Signal Processing & Multimedia

Yvon Savaria, École Polytechnique de Montréal, Canada Sergio Bampi, Instituto de Informatica UFRGS, Brazil Luc Claesen, University Hasselt, Belgium

### Track 7: EDA and CAD tools

Marie-Minerve Louërat, CNRS, LIP6, France Haidar Harmanani, Lebanese American University, Lebanon

### Track8: Energy Harvesting/Scavenging & Power Management

Aida Todri-Sanial, CNRS, LIRMM, France Emmanuel Bergeret, IM2NP, Université d'Aix-Marseille, France Aldo Romani, University of Bologna, Italy

### Track 9: Microsystems, Imaging, Sensors & Actuators

Luc Hébrard, INESS, Université de Strasbourg, France Maher Kayal, École polytechnique fédérale de Lausanne, Switzerland Wilfried Uhring, Université de Strasbourg, France

### Track 10: Digital Communications

Geneviève Baudoin, ESIEE, France Christoph Studer, Cornell University, USA

### Track 11: Circuits and Systems for Wireless and Wireline Applications

Frédéric Nabki, Université du Québec à Montréal, Canada José-Luis Gonzalez Jimenez, CEA-Leti, France Jean-Baptiste Begueret, IMS, Université de Bordeaux, France

### Track 12: Embedded and control systems

Suzanne Lesecq, CEA-Leti, France Michael Huebner, Ruhr-Universität Bochum, Germany

# Program at a glance

|               | Sunday, June 7 - Tutorial            | s - PHELMA                       |  |  |

|---------------|--------------------------------------|----------------------------------|--|--|

|               | Amphitheatre 001                     | Room 002                         |  |  |

| 8:30 - 10:00  | 1A                                   | 1B                               |  |  |

|               | Injection Locked Oscillators:        | FDSOI Technology - Part I - Body |  |  |

|               | Applications, Modeling & Design -    | Biasing techniques in UTBB       |  |  |

|               | Part I                               |                                  |  |  |

| 10:00 - 10:30 | Coffee break                         |                                  |  |  |

| 10:30 - 12:00 | Amphitheatre 001                     | Room 002                         |  |  |

|               | 2A                                   | 2B                               |  |  |

|               | Injection Locked Oscillators:        | FDSOI Technology - Part II -     |  |  |

|               | Applications, Modeling & Design -    | Millimeter Wave 28nm-CMOS FD     |  |  |

|               | Part II                              | SOI Power Amplifier Design       |  |  |

| 12:00 - 13:30 | Lur                                  | nch                              |  |  |

|               | Amphitheatre 001                     | Room 002                         |  |  |

|               | 3 <i>A</i>                           | 3B                               |  |  |

| 13:30 - 15:00 | Full Software Radio Circuits and     | Substrate Integrated Waveguides: |  |  |

| 13.30 - 13.00 | Systems: Design by Mathematics in    | from PCB to Microelectronics     |  |  |

|               | 28nm FDSOI Technology and            | Technologies - Part I            |  |  |

|               | Application to 5G Standard - Part I  |                                  |  |  |

| 15:00 - 15h30 | Coffee break                         |                                  |  |  |

|               | Amphitheatre 001                     | Room 002                         |  |  |

|               | 4 <i>A</i>                           | 4B                               |  |  |

| 45.00 47.00   | Full Software Radio Circuits and     | Substrate Integrated Waveguides: |  |  |

| 15:30 - 17:00 | Systems: Design by Mathematics in    | from PCB to Microelectronics     |  |  |

|               | 28nm FDSOI Technology and            | Technologies - Part II           |  |  |

|               | Application to 5G Standard - Part II |                                  |  |  |

| 18:30         | Welcome                              | reception                        |  |  |

| Monday, June 8 - MINATEC Conference Center |                                                            |                                    |                                    |  |  |

|--------------------------------------------|------------------------------------------------------------|------------------------------------|------------------------------------|--|--|

| 8:30 - 9:10                                |                                                            | Auditorium                         |                                    |  |  |

| 6.30 - 9.10                                |                                                            | Opening Ceremony                   |                                    |  |  |

|                                            |                                                            | Auditorium                         |                                    |  |  |

| 9:10 - 10:10                               | Plenary Lecture 1, J.Sifakis                               |                                    |                                    |  |  |

| 10:10 - 10:30                              | Coffee break                                               |                                    |                                    |  |  |

|                                            | Auditorium                                                 | Room 222                           | Room 224                           |  |  |

|                                            | 7A                                                         | 7B                                 | 7C                                 |  |  |

| 10:30 - 12:00                              | Phase Locked Loops and Circuits for                        | EDA/CAD tools                      | DSP and Multimedia Circuits and    |  |  |

|                                            | Optical Communications                                     |                                    | <b>Applications</b>                |  |  |

|                                            |                                                            |                                    |                                    |  |  |

| 12:00 - 14:00                              |                                                            | Lunch                              |                                    |  |  |

|                                            | Auditorium                                                 | Room 222                           | Room 224                           |  |  |

|                                            | 8 <i>A</i>                                                 | 8B                                 | 8 <i>C</i>                         |  |  |

| 14:00 - 15:30                              | Noise and Random Phenomena in                              | Digital Circuits and Architectures | Energy Harvesting: from Devices to |  |  |

|                                            | Analog Circuits                                            | for Processing                     | Systems                            |  |  |

|                                            |                                                            |                                    |                                    |  |  |

| 15:30 - 16:30                              | Coffee break                                               |                                    |                                    |  |  |

|                                            |                                                            | Grand Salon                        |                                    |  |  |

| 15:45 - 17:00                              | 9A Poster Session I 9B Meiji University Students' workshop |                                    |                                    |  |  |

|                                            | Auditorium                                                 | Room 222                           | Room 224                           |  |  |

|                                            | 10 <i>A</i>                                                | 10B                                |                                    |  |  |

| 1/1 20 10 00                               | Special Session Circuits and Systems                       | Special Session On-chip            |                                    |  |  |

| 16h30 - 18:00                              | for Medical Applications                                   | Measurements for Characterization, |                                    |  |  |

|                                            |                                                            | Testing, and Calibration of Analog |                                    |  |  |

|                                            |                                                            | Front-ends and mmW Devices         |                                    |  |  |

| 18:45                                      |                                                            | Coktail/Museum visit               |                                    |  |  |

| Tuesday, June 9 - MINATEC Conference Center |                                             |                                      |  |  |

|---------------------------------------------|---------------------------------------------|--------------------------------------|--|--|

| 9:00 - 10:00                                | Auditorium<br>Plenary Lecture 2, C. Fourtet |                                      |  |  |

| 10:00 - 10:30                               | Coffee break                                |                                      |  |  |

| 10:00 - 11:30                               | Grand Salon  12A Poster Session II          |                                      |  |  |

|                                             | Auditorium                                  | Room 222                             |  |  |

|                                             | 13 <i>A</i>                                 | 13B                                  |  |  |

| 10:30 - 12:00                               | Timing Variations and Resiliency            | Modeling, Design and Conditioning of |  |  |

|                                             |                                             | Sensing Devices                      |  |  |

| 12:00 - 13:30                               | Lunch                                       |                                      |  |  |

|                                             | Auditorium Room 222                         |                                      |  |  |

|                                             | 14A                                         | 14B                                  |  |  |

| 13:30 - 15:00                               | Wireless Transmitters and                   | Mixed Signal Circuits                |  |  |

|                                             | Receivers                                   |                                      |  |  |

| 15:00 - 15:20                               | Coffee break                                |                                      |  |  |

|                                             | Auditorium                                  | Room 222                             |  |  |

|                                             | 15A                                         | 15B                                  |  |  |

| 15:20 - 16:50                               | Voltage References and Power                | Special Session Approximate          |  |  |

|                                             | Converters                                  | Computing                            |  |  |

| 16:50 - 18:10                               |                                             | Auditorium                           |  |  |

|                                             | Panel Session                               |                                      |  |  |

| 18:30                                       | Gala Dinner                                 |                                      |  |  |

| 224<br>Cal Converters |  |  |  |

|-----------------------|--|--|--|

|                       |  |  |  |

| al Converters         |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

| Lunch                 |  |  |  |

| 224                   |  |  |  |

| ;                     |  |  |  |

| ntrol Techniques      |  |  |  |

| puting Systems        |  |  |  |

| J ,                   |  |  |  |

| Coffee break          |  |  |  |

| 224                   |  |  |  |

| ;                     |  |  |  |

| s Integration         |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

|                       |  |  |  |

# **Tutorials**Sunday 7<sup>th</sup> June 2015, PHELMA

# Tutorial 1: "Injection Locked Oscillators: Applications, Modeling, and Design"

Tony Chan Carusone (Integrated Systems Laboratory, University of Toronto, Canada) Sunday  $7^{th}$  June 2015 from 8:30 to 10:00 (Part I) and from 10:30 to 12:00 (Part II), Amphitheatre 001, Phelma

### **Abstract**

Injection-locked oscillators (ILOs) have experienced increasing use for wireless RF communication and in clocking circuitry for wireline links. This presentation begins with some background on ILOs, highlighting their benefits compared with DLLs, PLLs and other circuitry capable of clock amplification, multiplication, phase generation, interpolation, and phase noise filtering. A challenge limiting the practical use of ILOs in these applications is that their modeling is less well understood. This tutorial will therefore summarize the analysis and practical modeling methods for ILOs. First, the classical linearized model is presented. The intuitive understanding afforded by the linearized model will be highlighted and it will be used to inform high-level design choices. Second, the impulse sensitivity function, a cyclo-stationary approach popularized for modeling phase noise in oscillators, is applied to the modeling of ILOs. Finally, a more accurate model, called the phase transfer characteristic, is described, including methods for model extraction. A live demo of ILO modeling for practical applications will be incorporated into the tutorial using Matlab/Simulink.

The tutorial will then overview the design of ILOs for several practical applications. First, multi-phase clock generation is covered and techniques to ensure uniform spacing of the generated phases are described. Second, the use of ILOs for phase interpolation is discussed. A key challenge here is the ability to provide a clock phase programmable over the entire range  $\pm\pi$  radians. For example, some past work in this area has observed that an ILO's performance suffers when used for phase shifts exceeding  $\pm\pi/2$  radians. This problem may be addressed by selectively injecting either the in-phase or quadrature stage of a quadrature ILO, thereby providing an additional 90-degree phase shift. Implementations of this approach are described including both ring and LC oscillators operating at frequencies from 2 - 20 GHz in CMOS technologies from 65nm - 130nm. Finally, approaches towards the design of an ILO for clock multiplication are reviewed. Particular attention is paid to the need to ensure adequate lock range for frequency-agile applications. A useful approach in this regard is to ensure strong injection via multiple sites in the oscillator, demonstrated in a 4x multiplying ILO implemented in 40nm CMOS.

The tutorial will culminate in two detailed design case studies from the presenter's past work that combine multiple ILOs into highly-functional clocking subsystems. First, a high-

frequency jitter-tolerant receiver in 65 nm CMOS is presented. The clock receiver comprises two ILOs to frequency-multiply, deskew, and adjust jitter tracking bandwidth. Jitter tolerance is improved by tracking correlated jitter through the ILOs. Different data rates and latency mismatch between the clock and data paths are accommodated by controlling the ILOs' jitter tracking bandwidth up to 300 MHz. A receiver using this architecture in 65nm CMOS consumes 0.92 pJ/bit operating at 7.4 Gb/s and has a jitter tolerance of 1.5 UI at 200 MHz. Second, a frequency agile multiplying injection-locked oscillator (MILO) suitable for fast power cycling is presented. Edge detectors and multiple injection sites extend the aggregate lock range of two MILOs to 55.7% of the 3.16-GHz center frequency. Monitoring circuits identify the correct MILO and power-off the other within 10 reference clock cycles.

### Biography

Tony Chan Carusone received his Ph.D. at the University of Toronto in 2002. Since then, he has been with the Department of Electrical and Computer Engineering at the University of Toronto where he is currently a Professor and the department's Associate Chair, Research. He is a Senior Member of the IEEE, has co-authored the best paper at the 2005 Compound Semiconductor Integrated Circuits Symposium, the best student papers at the 2007, 2008, and 2011 Custom Integrated Circuits Conferences, and the best invited paper at the 2010 Custom Integrated Circuits Conference. He was the Editor-in-Chief of the IEEE Transactions on Circuits and Systems II: Express Briefs and a member of the Technical Program Committee for the International Solid-State Circuits Conference. He currently serves on the editorial board of the IEEE Journal of Solid-State Circuits and on the Technical Program Committee for the VLSI Circuits Symposium. He is a regular consultant to industry in the areas of analog, mixed-signal, and communication integrated circuit design, and is an author, along with David Johns and Ken Martin, of the 2nd edition of the classic textbook "Analog Integrated Circuit Design".

## Tutorial 2: "FDSOI Technology"

Philippe Flatresse (STMicroelectronics, Crolles, France), Eric Kerhervé, Aurélien Larie, Baudouin Martineau (IMS Laboratory, Bordeaux, France).

Sunday  $7^{th}$  June 2015, from 8:30 to 10:00 (Part I) and from 10:30 to 12:00 (Part II), Room 002, Phelma

#### **Abstract**

# - Part I: Body Biasing techniques in UTBB FDSOI technology (by Philippe Flatresse)

With the increasing demand of processing power to be delivered by the System On Chips, it is now key to improve their energy efficiency, not only for thermal or battery life duration purpose but also for environmental considerations such as green supercomputers, wireless base stations and micro servers. Using FD-SOI technology enables designing energy efficient SOCs running at very high frequency over an ultra-wide voltage range while minimizing power dissipation. In this context, STMicroelectronics has developed a full design platform leveraging on body biasing considered as the key design solution to provide best-in class SOCs to the market. The talk will describe the capability of body biasing, showing it is not only well suited for performance boosting but also for power optimization and compensation. Body biasing implementation details will be also shared thru the presentation of several silicon demonstrations.

# - Part II : Millimeter Wave 28nm-CMOS FD SOI Power Amplifier Design (by Eric Kerhervé, Aurélien Larie, Baudouin Martineau)

Traditionally, millimeter-wave (mmW) circuits using only III-V technologies have been used in low-volume, high-performance products. With the recent progress of highly scaled Sibased technologies such as 28nm-CMOS FD SOI achieving  $f_{\mathcal{T}}$  and  $f_{max}$  beyond 300 GHz, the application area of Si-based technologies has broadened from digital, analog, RF, and microwave domains to include mmW applications. The aim of this tutorial is to give the audience the design flow to successful the mmw power amplifier design in 28nm-CMOS FD SOI technology from STMicroelectronics. Recent developments at 60GHz perform by IMS Bordeaux will illustrate this tutorial from a research activity point of view.

Summary of the 60 GHz 28nm-CMOS FD SOI Power Amplifier design flow

- Why CMOS FD SOI?

- PA structure

- Challenge (active device)

- PA operating classes

- Linearity issues in WPAN applications

- Choice of structures and transistor topologies

- 28nm CMOS FD SOI transistor performances

- Optimal transistor finger width for  $f_{\text{max}}$

- Optimal biasing for  $f_{\mathsf{T}}$  and  $f_{\mathsf{max}}$

- Output power and number of transistor fingers

- 28nm CMOS FD SOI transistor design

- Optimum output impedance determination

- Impact of the parasitic interconnections

- Extraction of parasitic elements

- Stability issues

- Impedance matching network design

- Simulation and measurement results of the PA

### Biography

**Philippe Flatresse** received M.S. degree in Electrical Engineering in 1995 and PhD degree in Microelectronics in 1999 from Grenoble institute of technology. During his thesis, he has developed the LETISOI spice model dedicated to SOI technologies at CEA LETI, the R&D laboratory from French Atomic Energy Commission.

In year 2000, he joined STMicroelectronics Central R&D to deploy the SOI digital design within the company. He has developed the first SOI standard cells and SRAM libraries as well as IOs including innovative ESD solutions. He has also invented several dedicated CAD tools and low power digital design techniques such as power switches. Thanks to this work, he has pioneered the SOI technology and demonstrated its key advantages for low power high performance digital applications As a design architect, his current research activities are the exploration, development and implementation of ultra-low power platforms able to work in an energy-efficient way on an ultra-wide range of operating points targeting highgrowth application areas. His main objective is to explore the energy efficiency limits of parallel computing on multi-cores systems for ultra-low power processing by combining UTBB FD-SOI technology, advanced power management techniques, hardware accelerators and software infrastructure. His current role in ST is in the specification of the appropriate design solutions and technology variants for CMOS products in the following applications area: multimedia processors, consumer products, servers & routers, gaming, low power microcontrollers. His expertise covers bulk and SOI technologies, high performance energy efficient designs, design of libraries and IPs and silicon qualification. He has authored or co-authored more than 50 technical papers, and has filed more than 10 patents in advanced CMOS technologies.

Eric Kerhervé received the Ph.D. degree in Electrical Engineering from University of Bordeaux, France in 1994. He joined ENSEIRB-MATMECA and the IMS Laboratory in 1996, where he is currently Professor in Microelectronics and Microwave applications. His main areas of research are the design of RF, microwave and millimeter-wave circuits (power amplifiers and filters) in silicon GaAs and GaN technologies. He is or was involved in several European projects (Medea+ UPPERMOST, Medea+ QSTREAM, Catrene PANAMA, FP6 MOBILIS, ENIAC MIRANDELA), to develop silicon RF/mmW power amplifiers. He has authored or co-authored more than 190 technical papers in this field, and was awarded 23 patents. He has organized 8 RFIC and EuMC workshops on advanced silicon technologies for radiofrequency and millimeter-wave applications. He is involved in the technical program committees of various international conferences (ICECS, IMOC, NEWCAS, EuMIC, SBCCI, LASCAS) and he was the general co-chair of the international IEEE ICECS'2006 and IEEE NEWCAS'2011 conferences. He is co-editor of Special Issues for IEEE-ICECS'2006, IEEE-ICECS'2007, IEEE-LASCAS 2010. He was 2-years associate editor of IEEE Transactions on Circuits and Systems II (TCAS II). He is IEEE senior member and member of the IEEE-CAS, IEEE-MTT and IEEE SSCS societies.

# Tutorial 3: "Full Software Radio circuits and systems: Design by Mathematics in 28nm FDSOI technology and application to 5G standard"

Yann Deval, François Rivet, Yoan Veyrac, Nassim Bouassida (IMS Laboratory, Bordeaux, France).

Sunday 7<sup>th</sup> June 2015, from 13:30 to 15:00 (Part I) and from 15:30 to 17:00 (Part II) Amphitheatre 001, Phelma

### **Abstract**

The diversity of communication standard simplies the use of multi-band and multi-mode radios. Recent years have seen a wide Investigation on Software Defined Radio for Cognitive Radio application. But, this is always constrained to multi---standards prospectives while a complete agility of RF transceivers is required. That is why Full Software Radio proposes to challenge a new way of integrating RF circuits and systems by tackling the main issue: transceiving concurrently any RF signal within a very wide band of interest for telecommunication industry, from 0 to 5GHz for instance.

It is clearly observed that disruptive solutions are required. The focus of this tutorial will be on the design by mathematics of such RF transceiver design, exploring novel approaches along with a thorough discussion of advanced techniques for these receivers and transmitters towards a revolution in RF integrated circuits and systems. 28nm FDSOI technology from STMicroelectronics will be detailed to demonstrate its strengths in RFIC design. First, a frequency system is presented using a Sampled Analog Signal Processor as a receiver and a Walsh frequency combiner for the transmitter. Then, a temporal system is presented using a wide-band delta analog to digital converter as a receiver and a RF arbitrary waveform generator, named Riemann Pump for the transmitter. The methodology of every approach will be detailed following the same flow: mathematics, trade-off with RF electronics integration in 28nm FDSOI, architecture proposal, high level simulation results, circuit design issues, measurement results. Finally, an application to 5G standard will be addressed by demonstrating the feasibility of such systems to carrier aggregation, wideband capabilities, low power consumption and high order of modulation schemes.

### Table of content

The goal of this tutorial is to present our original methodology of Full Software Radio system design. The learning objectives address a wide audience:

- 1. beginner: presentation of RF constraints for circuit design, trade off between specification and 28nm FDSOI technologies.

- 2. intermediate: analog signal processing issues, noise, power, architecture.

- 3. advanced: mathematics adequation with transceiver specification, dynamic range, power consumption, technology.

Wireless system designers have been facing the continuously increasing demand for high data rates and mobility required by new wireless applications and therefore have started research on new generation of wireless systems that are expected to be deployed beyond 2020. For instance, 5G wireless networks will support 1,000-fold gains in capacity,

connections for at least 100 billion devices, and a 10 Gbps individual user experience capable of extremely low latency and response times. Deployment of these networks will emerge between 2020 and 2030. We present 3 main techniques:

- SASP Rx is a frequency domain receiver.

The principle of the SASP aims at selecting a spectral envelope of a RF signal within a very wide frequency band. To reach this target, the SASP processes analogically the RF input signal spectrum thanks to an analog Discrete Time Fourier Transform (DFT) with discrete time voltage samples. Once the spectrum is processed, voltage samples representing the spectral signal envelope to be treated are converted into digital. The selection of few voltage samples among thousands replaces the classical mixing and filtering operations. It reduces the A/D conversion frequency from GHz frequencies to MHz ones and thus allows a multi band selection at a very low power consumption. Its application for 5G standard is a direct carrier aggregation to achieve a 1Gbps data rate. SASP is a technique developed by IMS in 2010 by Rivet.

Walsh is a frequency domain transmitter.

The aim here is to generate any kind of waveform from its spectrum i.e. from its harmonics. For this, and similarly to the Fourier theory, Walsh transform allows decomposing any signal into a series of harmonics. But, instead of building this series on sine waves harmonics, Walsh theorem demonstrates that a family of square waves can generate any kind of signal. Thereby, using a millimeter-Wave [mmW] Phase-Locked Loop [PLL], the harmonic generation can be done at low power and area integration cost. It avoids the integration of several voltage controlled oscillators associated to each harmonics of the series. Indeed, square signals can be generated from a high frequency and divide by 2, N times thanks to a mmW PLL. The mathematical theory based on Walsh theorem states that using algebraic operations (phase shifting, sum, delay, ...) on a finite number of square waves allows to implement this signal generator. The originality of this project is that every square signals are directly amplified and then combined by their power to form the transmitted signal with a correct matching. The sum is performed thanks to a current node. Algebraic operations are consequently carried out by biasing differential amplifying square signals. Walsh is a technique developed by IMS in 2013.

- Riemann Pump is a time-domain transmitter.

The purpose of the Riemann Pump is to generate arbitrary waveforms up to the gigahertz range with a low cost and low consumption solution, the main target being the generation of modulated signals, especially to address the 5G standard. The wanted signal is to be generated thanks to a pre-determined set of slopes. At first, the Riemann code is computed from the theoretical desired signal; it corresponds to the slope index sequence giving the better approximation of the signal (within the meaning of the Riemann integral). This code controls switched current sources, in order to produce current steps that are integrated into an output capacitive load, thus generating a piecewise linear approximation of the wanted signal. Riemann is a technique developed by IMS in 2013.

### Biography

Yann DEVAL received his PhD from the University of Bordeaux, France, in 1994. He joined this university in 1993 as an Assistant Professor. In 1999 Pr. Deval became an Associate

Professor and created the IC Design Team at IMS. In 2004 he became a Full Professor at ENSEIRB MATMECA. From 2006 to 2010 Pr. Deval was the head of IC Design Group at IMS. Also, from 2010 to 2012 Pr. Deval was the Director of ALBATROS, the advanced research alliance between THALES and the University of Bordeaux for aeronautics and space applications, and since January 2007 he is the Director of ST IMS collaborative joint research laboratory. He was the General Chair of the 2010 RFIC Symposium in Anaheim, CA, and the General Chair of the 2012 ESSCIRC ESSDERC conferences in Bordeaux, France. Pr. Deval published more than 170 papers in international conferences and journals, and holds 46 patents.

Francois RIVET received the PhD degree in 2009 from the University of BORDEAUX, France. Since June 2010, he is tenured as Associate Professor at Bordeaux Institute of Technology and IMS Lab, the microelectronics laboratory of the University of BORDEAUX. His research is focused on the design of RFICs. Dr. Rivet has publications in top ranked journals (JSSC, TCAS-II), international conferences (RFIC, RWS), national conferences (JNM) and holds 9 patents. He received the Best Paper Award at Software Defined Radio Forum in 2008 at Washington DC, USA.

**Yoan VEYRAC** received the Master degree in 2012 from the Electrical Engineering School of Bordeaux, France (ENSEIRB-MATMECA). He is currently pursuing the PhD degree at the IMS laboratory (Bordeaux), in the circuits and systems team. He is specialized in RF architectures and circuit design, especially in the field of software radio transmitters.

Nassim BOUASSIDA received the Master degree in 2012 from the University of BORDEAUX, France. He is with STMicroelectronics as a hardware engineer and PhD student at the IMS laboratory (Bordeaux), in the Circuits and Systems team. He is currently working on software radio transmitters.

# Tutorial 4: "Substrate Integrated Waveguides: from Early Printed-Circuit Board Processing to Future Smart and Active Material Integration"

Ke WU (Poly-Grames Research Center, Department of Electrical Engineering Center for Radiofrequency Electronics Research of Quebec (CREER), Polytechnique Montréal, Québec, Canada H3T 1J4).

Sunday  $7^{th}$  June 2015, from 13:30 to 15:00 (Part I) and from 15:30 to 17:00 (Part II) Room 002, Phelma

### **Abstract**

Recent research effort in exploring and exploiting substrate integrated circuits (SICs) has fundamentally changed the landscape of high-frequency circuit and system integration and development. In particular, substrate integrated waveguide (SIW) technology, which is part of the SICs family, has created a great enthusiasm in the applied electromagnetic and integrated circuit community worldwide for a wide range of low cost-enabled commercial and high-performance-oriented defense applications from MHz to THz. The critical enablers in this disruptive technology lie in the successful hybrid and monolithic planarization and integration of non-planar metallo-dielectric waveguides through the structure synthesis made of various processing techniques. The early SIW technology development has been pushed forward and has become matured thanks to the development of a series of single layered and multi-layered printed circuit board (PCB) processing techniques and hybrid multilayered micro-fabrication processing techniques such as LTCC and photo-imageable processing techniques. Those fabrication techniques have contributed to the fast-paced progress of passive integrated components, circuits and antennas. This paper reviews the recent developments and accomplishments of various SIW antenna and circuit techniques with emphasis on PCB-based design platforms. Practical examples are shown for their applications in the design and development of innovative integrated passive circuits and antenna arrays for applications ranging from MHz to THz. Emerging and future development trends of SIW techniques are discussed with special interest in the use and integration of smart and active materials as well as semiconductor-based microelectronic processing techniques such as CMOS schemes over millimeter-wave and terahertz frequency ranges. It is anticipated that emerging CMOS-based "SIW and SICs" will prevail in the decades to come. This presentation will also deal with a number of grand challenging issues and the arising of unprecedented problems in passive-active circuits integrations.

### Biography

**Ke Wu** is Professor of electrical engineering, and Canada Research Chair in RF and millimeter-wave engineering at the Ecole Polytechnique (University of Montreal). He has been the Director of the Poly-Grames Research Center and the Founding Director (2008-2014) of the Center for Radiofrequency Electronics Research of Quebec. He held/holds visiting/honorary professorships at various universities in the world. He has authored/co-authored over 1000 referred papers, and a number of books/book chapters and more than 30 patents. Dr. Wu has held key positions in and has served on various panels and

international committees including the chair of technical program committees, international steering committees and international conferences/symposia. In particular, he was the general chair of the 2012 IEEE MTT-S International Microwave Symposium. He has served on the editorial/review boards of many technical journals, transactions and letters as well as scientific encyclopedia including editors and guest editors. He has been providing consulting services to corporations, governments and universities around the world. Dr. Wu is an elected IEEE MTT-S AdCom member and has served as the chair of many standing committees including Transnational Committee, Member and Geographic Activities (MGA) Committee and Technical Coordinating Committee (TCC). He is the 2015 IEEE MTT-S President-Elect and will become the 2016 IEEE MTT-S President. He also serves as the inaugural North-American representative in the General Assembly of the European Microwave Association (EuMA). He was the recipient of many awards and prizes including the inaugural IEEE MTT-S Outstanding Young Engineer Award, the 2004 Fessenden Medal of the IEEE Canada, the 2009 Thomas W. Eadie Medal from the Royal Society of Canada (The Academies of Arts, Humanities and Sciences of Canada), the Queen Elizabeth II Diamond Jubilee Medal, the 2013 Award of Merit of Federation of Chinese Canadian Professionals, the 2014 IEEE MTT-S Microwave Application Award, the 2014 Marie-Victorin Prize (Prix du Québec - the highest distinction of Québec in the Natural Sciences and Engineering) and the 2015 "Prix d'excellence en recherche et innovation" of Polytechnique Montreal. He is a Fellow of the IEEE, a Fellow of the Canadian Academy of Engineering (CAE) and a Fellow of the Royal Society of Canada. He was an IEEE MTT-S Distinguished Microwave Lecturer from Jan. 2009 to Dec. 2011.

## Keynotes speakers

Keynotes 1: "The Internet of Things - The Ultimate ICT Revolution"

Joseph Sifakis - CRI Grenoble, Professor at EPFL

Monday, June 8th from 09:10 to 10:10 Auditorium, Minatec

#### **Abstract**

The Internet of Things (IoT) is a vision born from the convergence between embedded and networking technologies. It refers to the interconnection of uniquely identifiable embedded computing devices within the existing Internet infrastructure. Things can refer to a wide variety of devices such as heart monitoring implants, biochip transponders, automobiles with built-in sensors, field operation devices, smart thermostat and home appliances. They are equipped with sensors, actuators and microcontrollers which can provide the "real-time" embedded processing that is a key requirement of most IoT applications. The collected data are made available through a unified networking infrastructure, to users and interconnected machines. Furthermore, they can be processed and analyzed by the cloud for decision-making in order to respond to changes quickly and accurately, to predict events and optimize resources.

We shortly discuss the IoT vision and its feasibility. We show that its achievement challenges our capacity to design mixed hardware-software systems that are trustworthy and optimal. We advocate the need for rigorous system design techniques. We present the current state of the art and discuss three major scientific problems: 1) linking physicality and computation; 2) component-based systems engineering; 3) intelligence in particular as the ability of system adaptation in order to meet given requirements in the presence of uncertainty.

Achieving the IoT vision will have a tremendous societal, technological and scientific impact. In particular, it will reinvigorate Computing and enrich the discipline with new scientific foundations.

Joseph Sifakis is Emeritus Senior Researcher at CNRS, full professor at Ecole Polytechnique Fédérale de Lausanne (EPFL) and the director of "Centre de la Recherche Intégrative" (CRI) in Grenoble. His current research interests cover fundamental and applied aspects of embedded systems design. The main focus of his work is on the formalization of system design as a process leading from given requirements to trustworthy, optimized and correct-by-construction implementations. Joseph Sifakis is the founder of the Verimag laboratory in Grenoble, which he directed for 13 years. Verimag is a leading research laboratory in the area of embedded systems, internationally known for the development of the Lustre synchronous

language used by the SCADE tool for the design of safety-critical avionics and space applications. In 2007, Joseph Sifakis has received the Turing Award for his contribution to the theory and application of model checking, the most widely used system verification technique today. Joseph Sifakis has had numerous administrative and managerial responsibilities both at French and European level. He has actively worked to organize the European research community in embedded systems as the scientific coordinator of the « ARTIST » European Networks of Excellence, for ten years. He has participated in many major industrial projects led by companies such as Airbus, EADS, France Telecom, Astrium, and STMicroelectronics.

Joseph Sifakis is a member of the French Academy of Sciences, a member of the French National Academy of Engineering and a member of Academia Europea. He is a Grand Officer of the French National Order of Merit, a Commander of the French Legion of Honor. He has received the Leonardo da Vinci Medal in 2012.

# Keynotes 2: "Circuit Techniques for next Generation Wireless Communication"

Bram Nauta - University of Twente, The Netherlands

Wednesday, June 10<sup>th</sup> from 10:50 to 11:50 Auditorium, Minatec

#### **Abstract**

Due to the increase of wireless standards using different RF frequencies there is a need to have transceivers that can handle a wide range of RF frequencies.

By abandoning the classical narrowband approach, new receiver architectures are explored in which noise and interferer robustness problems have to be solved. At the same time new features are wanted such as spectrum sensing for cognitive radio and self-interference cancelling for future full duplex communication. In this presentation several circuit and system techniques will be illustrated that may enable future radio systems.

Bram Nauta was born in 1964 in Hengelo, The Netherlands. In 1987 he received the M.Sc degree (cum laude) in electrical engineering from the University of Twente, Enschede, The Netherlands. In 1991 he received the Ph.D. degree from the same university on the subject of analog CMOS filters for very high frequencies. In 1991 he joined the Mixed-Signal Circuits and Systems Department of Philips Research, Eindhoven the Netherlands. In 1998 he returned to the University of Twente, as full professor heading the IC Design group. His current research interest is high-speed analog CMOS circuits, software defined radio, cognitive radio and beamforming.

He served as the Editor-in-Chief (2007-2010) of the IEEE Journal of Solid-State Circuits (JSSC), and was the 2013 program chair of the

International Solid State Circuits Conference (ISSCC). Also he served as Associate Editor of IEEE Transactions on Circuits and Systems II (1997-1999), and of JSSC (2001-2006). He was in the Technical Program Committee of the Symposium on VLSI circuits (2009-2013) and is in the steering committee and programme committee of the European Solid State Circuit Conference (ESSCIRC). Moreover he is member of the ISSCC Executive committee. He served as distinguished lecturer of the IEEE, is elected member of IEEE-SSCS AdCom and is IEEE fellow. He is co-recipient of the ISSCC 2002 and 2009 "Van Vessem Outstanding Paper Award" and in 2014 he received the 'Simon Stevin Meester' award (500.000€), the largest Dutch national prize for achievements in technical sciences. In the same year he has been appointed as distinguished professor at the University of Twente.

# Keynotes 3: "The technical challenges of future IoT networks and their consequences on modem's and SoC's design" Christophe Fourtet - SigFox, France

Tuesday, June 9th from 9:00 to 10:00 Auditorium, Minatec

### **Abstract**

IoT or « Internet of Things », recognized as the future massive extension of "M2M", will become one of the major markets of the following years and is going to bring incredible revolutions in industrial, and generally speaking, human activities, like energy, resource management, necessary replacement of programmed obsolescence by predictive maintenance or "on demand improvements" of machines, health care improvements, optimized agriculture...etc...

For those revolutions to come true, beyond necessity of other ongoing breakthrough on materials, nano-tech, or sensors, the IoT telecom revolution itself needs to be a reality. This is the big challenge. Because an unprecedented density of devices, at very low cost, with outstanding needs for autonomy, that humanity will have to "forget" along their service after "dissemination" on the field, will require a complete "flip-over" of the philosophy that has been dominating in the telecom industry for 100 years, with a culminating point in modern radiotelephony and internet.

Networks are today massively forcing their "administrated" modems to be highly disciplined (in frequency or modulation accuracy, time synchronization...) before they can negotiate a single bit of data. For a working IoT world, networks will need to be switched to "highly cognitive", with a high capacity to dynamically adapt to the various behavior of the disseminated devices they will have to "serve", through massively parallel Software Defined principles.

"Networks at the service of free devices": A true historic revolution in telecoms in fact!

Those philosophy changes will have unprecedented consequences on the modem's properties that will be embedded in those famous "objects", and thus will have consequences on hardware as well as software components from which they will be built. By cascade effect, consequences on SoC definition and design, will not be of minor importance...

Graduated from INSA de Lyon and holds a DEA in electromagnetism, Christophe Fourtet is a long time enthusiast of science and technology, particularly radio and electromagnetism. This passion will take him to work on multiple radio projects in companies such as Thomson, TALCO, SAGEM, MOTOROLA, as a design engineer and as a technical manager. He has been working on topics such as PMR, then pioneering digital PMR as well as digital cellular, and then 3G / LTE. In fact, caught in the 90s as many radio specialists by the wave of cellular and its quest of broadband, he made a 180 degree turn

starting to work on more "frugal" and "low footprint" radio systems, combining low power and high performance for a given service.

The modern UNB (Ultra Narrow Band) began to be born, and it is his meeting with Ludovic Le Moan, that triggered the spark of SIGFOX five years ago.

### Special Sessions

### 1-CIRCUITS AND SYSTEMS FOR MEDICAL APPLICATIONS

Organizers: Dr. Guillaume Charvet (CEA, France)

### Monday June, 8th, from 16:30 to 18:00, Room Auditorium

#### Abstract:

Recent advances in the field of integrated circuits design and systems have been open new opportunities for the design of innovative medical devices. This special session focuses on the design of medical devices based on innovative circuits and the targeted medical applications.

The design of medical devices needs to respect a lot of constraints such as ultra-low power, miniaturization, safety and reliability. Moreover, in order to go to clinical trials, the medical device needs to satisfy all the regulatory requirements. Taking into account all these constraints at the earliest in the design of a medical device is essential.

Likewise, this special session aims to provide a vision of the future needs of technological bricks and the associated constraints, in order to design the future generations of medical devices.

### Papers:

"Low-Power Radar Techniques for Remote Sensing and Detection of Vital Signs"

K. Wu

University of Montreal, Canada

"A wireless fully implantable ECoG recording medical device WIMAGINE®: from the design of an integrated circuit toward a clinical trial"

G. Charvet, C. Mestais, F. Sauter-Starace, M. Foerster, A. Lambert, C. Chabrol, S. Robinet, R. D'Errico, V. Josselin, N. Torres-Martinez, T. Costecalde, D. Ratel, A.L. Benabid CEA-LETI, Grenoble, France

"Advanced Active Implantable Medical Devices how to get the best trade off between research needs and clinical usability"

D. Guiraud (IEEE EMBS Member), G. Cathébras (IEEE Member), D. Andreu INRIA, Montpellier University, France

# 2-ON-CHIP MEASUREMENTS FOR CHARACTERIZATION, TESTING, AND CALIBRATION OF ANALOG FRONT-ENDS AND MMW DEVICES

Organizers: Jean-Daniel Arnould (IMEP-LAHC); Haralampos-G. Stratigopoulos (TIMA Labs, France)

Monday June, 8th, from 16:30 to 18:20, Room 222

### Abstract:

The purpose of the special session is to discuss state-of-the-art on-chip measurement methods in the context of characterization of mmW devices and testing and calibration of analog, mixed-signal, and RF integrated circuits. The need for low-overhead, non-intrusive, and reliable on-chip measurement methods is dictated by (a) the heterogeneity and complexity of modern mixed analog-digital systems-on-chip and systems-in-package that offer very limited controllability and observability from the output pins in order to perform testing; (b) the increased process variations in advance technology nodes (e.g. 65nm and beyond) that make post-manufacturing calibration of outmost importance in order to correct yield loss; (c) safety-critical and mission-critical systems that need to be equipped with on-chip self-calibration mechanisms for detecting early reliability hazards and applying self-corrective actions (e.g. fault tolerance, self-repair, etc.); and (d) the numerous modern applications of high-frequency devices (e.g. RF, mmW) whose accurate characterization and post-silicon verification requires to rely on on-chip test structures, since extracting signals off-chip for processing seriously degrades the measurement accuracy. This special session will gather together worldwide experts on the above research fields to share with the conference attendees the most recent and state-of-the-art solutions proposed to date.

### Papers:

### "Self-healing of RF circuits using built-in non-intrusive sensors"

Martin Andraud, Haralampos-G. Stratigopoulos, and Emmanuel Simeu, TIMA Laboratory, Grenoble, France

### "150 GHz load pull measurements on BiCMOS 55nm SiGe: C HBT using in situ tuner "

Alice Bossuet<sup>1,2,3</sup>, Thomas Quemerais<sup>2</sup>, Estelle Lauga-Larroze<sup>1</sup>, Jean-Michel Fournier<sup>1</sup>, Christophe Gaquière<sup>3</sup>

- <sup>1</sup>IMEP-LAHC, France

- <sup>2</sup> STMicroelectronics, France

- <sup>3</sup> IEMN, France

### "Integrated Test Concepts for In-Situ Millimeter-Wave Device Characterization"

- D. Kissinger <sup>1,2</sup>, J. Nehring <sup>3</sup>, A. Oborovski <sup>3</sup>, K. Borutta <sup>3</sup>, I. Nasr <sup>4</sup>, B. Laemmle <sup>5</sup>, R. Weigel <sup>3</sup>

- <sup>1</sup> IHP, Im Technologiepark Frankfurt, Germany

- <sup>2</sup> Technische Universität Berlin, Berlin, Germany

- <sup>3</sup> Institute for Electronics Engineering, Erlangen, Germany

- <sup>4</sup> Infineon Technologies, Neubiberg, Germany

- <sup>5</sup> Intel, Neubiberg, Germany

### "Embedded Instruments for Enhancing Dependability of Analogue and Mixed-Signal IPs"

Jinbo Wan and Hans G. Kerkhoff

TDT, CTIT, University of Twente, Netherlands

### "Substrate-Coupling effect in BiCMOS technology for millimeter wave applications"

- 5. Fregonese<sup>1</sup>, R. D'Esposito<sup>1</sup>, M. De Matos<sup>1</sup>, A. Köhler<sup>2</sup>, C. Maneux<sup>1</sup>, T. Zimmer<sup>1</sup> (IEEE Member)

- <sup>1</sup> CNRS-UMR 5218, University of Bordeaux, Talence, France.

### "Calibration and Characterization Techniques for On-Wafer Device Characterization."

L. Galatro and M. Spirito,

Electronics Research Laboratory/DIMES, Delft University of Technology, Delft, The Netherlands

### 3-APPROXIMATE COMPUTING

Organizers: Prof. Amara Amara (ISEP, Paris), Prof. Andreas Burg (EPFL, Lausanne) Tuesday June, 9th, from 15:20 to 16:50, Room 222

#### Abstract:

Motivation: CMOS technology is approaching its physical limits which manifests itself in diminishing returns from scaling in terms of speed and power consumption. Furthermore, reliability issues and uncertainties require more and more overhead for protection and larger guardbands to always ensure 100% reliable operation.

Topic: Approximate computing is a brand new design paradigm that has recently emerged as a potential solution to i) provide further improvements in speed and energy efficiency beyond scaling and ii) to deal with variability and reliability issues in advanced process nodes. While approximate computing comprises a wide range of techniques and ideas, it generally refers to the principle of relaxing the accuracy requirement on computations based on circuit-level considerations. Due to its highly vertical nature, the topic is extremely interdisciplinary and appears in a wide range of research communities, ranging from devices to VLSI circuits and architectures, to design automation/CAD, all the way to signal processing. Need for a special session at NEWCAS: In particular, in the design automation community, approximate computing and the issues related to reliability and variability have emerged over the last 3-4 years as one of the most prominent topics. Design automation conferences usually have corresponding tracks that discuss related design methodologies. However, we believe that there is also a very important circuit and systems component that is a very good match with the target audience of the NEWCAS conference. To highlight and discuss this component, we propose this special session for NEWCAS 2015 with a number of contributions from well-known experts in the field.

### Papers:

"A Scalable Model for Timing Error Prediction under Hardware and Workload Variations" X. Jiao¹, A. Rahimi¹, B. Narayanaswamy¹, H. Fatemi², J. Pineda de Gyvez², and R. K. Gupta¹ ¹CSE, UC San Diego, ²NXP Semiconductors

### "Approximate Computing with Unreliable Dynamic Memories"

- S. Ganapathy<sup>1</sup> A. Teman<sup>1</sup> R. Giterman<sup>2</sup> A. Burg<sup>1</sup> G. Karakonstantis<sup>3</sup>

- <sup>1</sup> EPFL, Switzerland

- <sup>2</sup> ENICS Lab, Faculty of Engineering, Bar Ilan University, Ramat Gan, Israel

- <sup>3</sup> High Performance and Distributed Computing, Queen's University Belfast, UK

<sup>&</sup>lt;sup>2</sup> Franhöfer Institute, Dresden, Germany

### "Energy Efficient Digital Design through Inexact and Approximate Arithmetic Circuits"

Vincent Camus, Jeremy Schlachter, Christian Enz EPFL, Switzerland

# "Near-Threshold Computing for Very Wide Frequency Scaling: Approximate Adders to Rescue Performance"

Soares, L. B.1; Bampi, Sergio1,2; Rosa, A.L.R2; Costa, E.A.C3.

<sup>1</sup> Graduate Program on Microelectronics (PGMicro)

<sup>2</sup> PPGC - Informatics Institute

Federal University of Rio Grande do Sul (UFRGS)

<sup>3</sup> Catholic University of Pelotas (UCPEL)

Porto Alegre, Brazil

### "Stochastic Computation With Spin Torque Transfer Magnetic Tunnel Junction"

L. Alves de Barros Naviner<sup>1</sup>, H. Cai<sup>1</sup>, Y. Wang<sup>1</sup>, W. Zhao<sup>2,3</sup>, A. Ben Dhia<sup>1</sup>

- <sup>1</sup> Institut Mines-Telecom, Telecom-ParisTech, Paris, France

- <sup>2</sup> IEF, Univ. Paris-Sud 11, Orsay, France

- <sup>3</sup> Beihang University, China

### 4-CONTROL TECHNIQUES FOR ADAPTIVE COMPUTING SYSTEMS

Organizers: Edith Beigné, Suzanne Lesecq, Anca Molnos (CEA, France)

Wednesday June, 10th, from 13:30 to 15:00, Room 224

### **Abstract**

Today mobile systems face strong constraints, especially regarding power consumption and thermal aspects while their performances are still increasing. To answer these new challenges, designers of circuits (analog, digital and mixed-signal, but also RF, MEMS) implement their circuits with some "adaptivity" features. For instance, part of the circuit will automatically adapt its parameters in order to reach the most effective functioning point from a performance versus consumption point of view. Dynamic Voltage and Frequency Scaling techniques can be seen as adaptive approaches that provide to the circuit just enough energy to perform the task it has to do, no more! However, advanced technologies, e.g. FDSOI ones, enlarge the design and functioning space with new parameters to be fixed either at design-time or at run-time. Other teams try to implement event-based approaches in order to make the circuit working only when mandatory.

However, these adaptive capabilities may have counterproductive effects if their design does not take into account (among others) stability and robustness issues. Techniques from the control community may help to answers these issues. The special session will provide an overview of such control techniques applied to adaptive systems, especially, but not limited to, regarding resource management, adaptable middleware, automatic control methods for energy/power reduction, seamless reconfiguration of algorithms and computing systems.

### **Papers**

### "Energy-efficient control through power mode placement with discrete DVFS and Body Bias",

Y. Akgul<sup>1</sup>, D. Puschini<sup>1</sup>, L. Vincent<sup>2</sup>, P. Benoit<sup>3</sup>, M. Altieri-Scarpato<sup>1</sup>

<sup>1</sup> CEA, LETI, Grenoble, France

<sup>2</sup> Labex PERSYVAL-Lab, Grenoble University

<sup>3</sup> LIRMM, University of Montpellier 2, Montpellier, France

# "A distributed synchronization of all-digital PLLs network for clock generation in synchronous SOCs".

C. Shan<sup>1</sup>, E. Zianbetov<sup>1</sup>, F. Anceau<sup>1</sup>, O. Billoint<sup>2</sup>, D. Galayko<sup>1</sup>

<sup>1</sup> Laboratoire d'informatique de Paris 6 (LIP6) – University of Pierre and Marie Curie (UPMC), Paris, France

<sup>2</sup> CEA-LETI, Grenoble, France,

### "Adaptive Computing in Real-Time Applications",

B. Janßen, F. Schwiegelshohn, M Hübner

Embedded Systems for Information Technology, Ruhr-University Bochum, Bochum, Germany

### "Autofocus performance realization using automatic control approach",

M. Zarudniev<sup>1</sup>, A. Tonda<sup>1</sup>, L. Alacoque<sup>1</sup>, S. Bolis<sup>2</sup>, A. Pouydebasque<sup>2</sup>, F. Jacquet<sup>2</sup>

<sup>1</sup> CEA-LETI Grenoble, France

<sup>2</sup> Wavelens, Grenoble, France

### "WSN Power Management with Battery Capacity Estimation",

O. Mokrenko<sup>1</sup>, M.-I. Vergara-Gallego<sup>1</sup>, W. Lombardi<sup>1</sup>, S. Lesecg<sup>1</sup>, C. Albea<sup>2</sup>

<sup>1</sup> CEA, LETI, Grenoble, France

<sup>2</sup> CNRS, LAAS, Toulouse France

### MEIJI UNIVERSITY STUDENTS'WORKSHOP

### Monday, June 8th from 15:45 to 17:00, room Grand Salon

The NewCAS 2015 conference runs the 3rd Edition of the ISEP-Meiji University students' workshop.

This workshop aims to support the cooperation between both institutions and to develop skills and competences needed in the research field for graduate students. The students follow the entire research flow: bibliographic study, research work, paper writing, poster/slides preparation and presentation in English are a good way to attract talent in research.

This year, eleven students from Meiji University and two PhD students from ISEP will present their research works during NEWCAS poster sessions. Their research topics include, but are not limited to analog filters, VCO, UWB radar, radio communication systems, Amplifiers...

The NewCAS organizing committee invites all attendees to visit this students' workshop and to discuss with the authors.

### Panel Session

# IoT Revolution : What is the key enabler? Technology, Software or Application

Tuesday, June 9th 2015 from 16:50 to 18:10, Auditorium, Minatec

### Panel Moderator:

Didier Belot (Engineer, CEA LETI)

### Panelists:

- Joseph Sifakis ( Director, EPFL )

- Yann Deval (Professor, IMS)

- Bram Nauta (Professor, UNIVERSITY OF TWENTE)

- Christophe Fourtet (CTO, SigFox)

- Remy Pottier (Director, ARM)

### Abstract:

The Internet of Things (IoT) is the network of physical objects or "things" embedded with electronics, software, sensors and connectivity to enable it to achieve greater value and service by exchanging data with the manufacturer, operator and/or other connected devices. Each thing is uniquely identifiable through its embedded computing system but is able to interoperate within the existing Internet infrastructure." This is the definition given by "Wikipedia".

Could we have a look on key words embedded in this definition?

The things are globally any objects, (any animal? Any persons?), which is connected to the web through a wireless (or rarely wireline) connectivity exchanging Private or Public data, coming from physical sensors with or without soft post processing, with other Internet users.

A list of questions coming from this definition are opened:

How can we supply such devices which are not plugged?

How can we sort out the good data to be sent, to be stored?

How can we manage the multiple connectivity standards?

How can we guaranty the privacy?

Where will be stored the information?

How can we reduce the global consumption increasing connected devices?

Which application(s) will be the driver of such network?

What will be the public acceptance, and why?

Finally which will bring the answer to these questions, the technology? The Software? The applications? A mix of all? Or other Key enablers?

### General information

### Registration desk schedule

Registration desk on site will be opened: Sunday, June 7<sup>th</sup> 2015, from 8:00 to 17:00 at Phelma Monday, June 8<sup>th</sup> 2015, from 8:00 to 18:00 at Minatec Tuesday, June 9<sup>th</sup> 2015, from 8:30 to 18:00 at Minatec Wednesday, June 10<sup>th</sup> 2015, from 8:30 to 17:00 at Minatec

### **Workshop Tutorial**

Sunday, June 7<sup>th</sup> 2015: Phelma Minatec

### Information

Any request for information of a general nature can be addressed to registration desk. Messages can be left at the registration desk; delegates will not be disturbed during the session excepted for emergencies.

### Technical support

Every room is equipped with a computer and a LCD projector. Should you need any technical assistance, please contact the registration desk prior to your presentation. For oral presentation a station will be set up to test your presentation files.

### Special notes for presenters

To ensure smooth running sessions, we recommend the following:

Lecture presenters must be present in the session room at least 10 minutes before the beginning, and the presentation files must be loaded onto the computer before the session starts. Each presentation will last 15 minutes followed by a 3 minutes period to allow for questions and brief discussions.

Poster presenters must have their poster set-up and removed according to the schedule of the sessions they have been assigned to.

### Poster set-up and removal schedule

Monday, June 8<sup>th</sup> 2015: Set-up: 15:00 to 15:30 Removal: 17:00 to 17:30

Tuesday, June 9<sup>th</sup> 2015: Set-up: 8:30 to 10:00 Removal: 11:30 to 13:00

# Special events of this conference

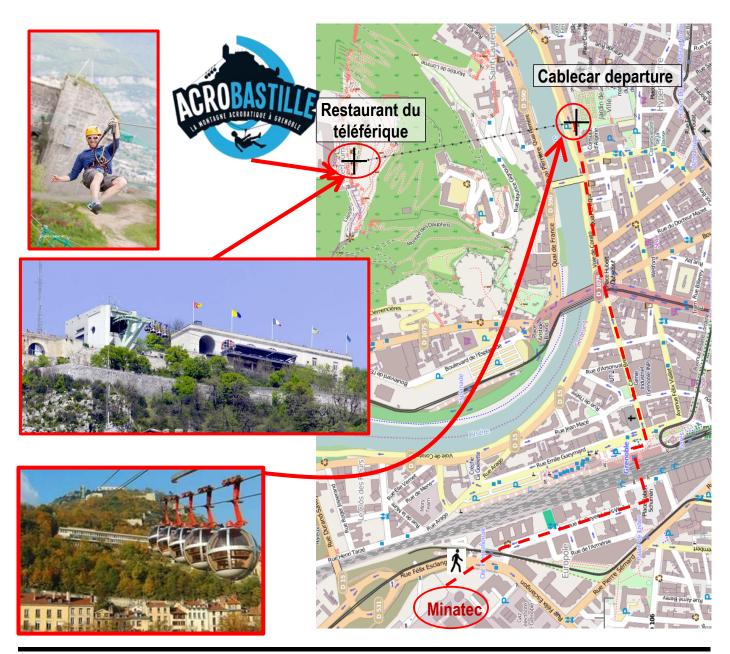

**Outdoor activity "Acrobastille":** close to the "restaurant du téléférique", La Bastille, Sunday, June 7<sup>th</sup> 2015 between 18:00 to 19:30.

Discover the Fort with a zip-line overflying the fortifications, and overcome balance games traps: certainly the best introduction to Grenoble! Please note that sportswear and trainers are recommended and that, if you're afraid of heights, you might jump directly to the welcome cocktail!

**Welcome reception:** "restaurant du téléférique", La Bastille, *Sunday, June 7<sup>th</sup> 2015 at 19:00* From the terrace, enjoy the view over the whole city and don't forget to hydrate yourself! Note that the cable car will close at 21:00.

Opening ceremony: Minatec, Monday, June 8th 2015 between 09:10-10:10

Coktail/museum visit: Musée de Grenoble, Monday, June 8th 2015 at 18:45

From 18:45 to 19:30 : Guided tour of the gallery

From 19:30 to 20:30: Welcome speech by Mr le Maire de Grenoble and buffet

The NEWCAS 2015 cocktail will take place at Grenoble Museum. With its collections of ancient, modern and contemporary art, the Musée de Grenoble offers you a chance to traverse the history of western painting from the  $13^{th}$  to the  $20^{th}$  centuries. Included are major masterpieces of classical Flemish, Dutch, Italian and Spanish painting; one of  $20^{th}$  century Europe's richest collections.

All the NEWCAS 2015 attendees will have the opportunity to discover an exceptional temporary exhibit, entitled *From Picasso to Warhol*, where the museum exposes its last acquisitions of the decade. The exhibition present a collection, wealthy and varied, of 150 works of different types as paintings, sculptures, photographs... Mainly of the 20th century but also other previous works. The two focal points of the exhibition are obviously *Verre* (1914) -a rare cubist collage- by Picasso and *Jackie* by Warhol. However, there are many other interesting works of art in the gallery that guides will present you.

Gala dinner: Chateau de Sassenage, Tuesday, June 9th 2015 at 19:00

Closing ceremony: Minatec, Wednesday, June 10<sup>th</sup> 2015 between 16:50-17:20

## Outdoor activity "Acrobastille" / Welcome reception

## "La Bastille" Restaurant du téléférique Sunday, June 7<sup>th</sup> 2015 at 19:00

"La Bastille". It is a small fortified mountain located at the crossroad of three valleys, served by the first urban cable-car in the world. There you will discover the flattest town in France in its mountain setting! When the sunsets and the lights go down in the city, the view is outstanding

How to go to La Bastille: you can take the cablecar, Quai Stéphane Jay, 15 minutes walk from Minatec. "Les bulles" (nickname of the cablecar) will take you to the top of the hill, 20 meters from the "restaurant du téléférique". Note that, before 17:30, cablecar tickets can be withdrawn at the conference registration desk.

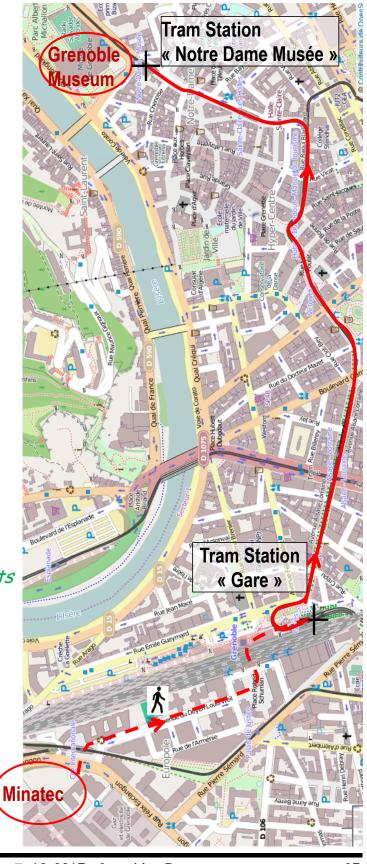

## Coktail / Museum visit

# Grenoble Museum Monday, June 8<sup>th</sup> 2015 at 18:45 Sponsored by the town council "Mairie de Grenoble"

With its collections of ancient, modern and contemporary art, the Musée de Grenoble offers you a chance to traverse the history of western painting from the 13th to the 20th centuries. Included are major masterpieces of classical Flemish, Dutch, Italian and Spanish painting; one of 20th century Europe's richest collections

# To go to the Cocktail/Museum By tram:

Take the tram B at the tram station "Gares" in direction of *Gières-plaine des sports* Stop at the tram station

"Notre Dame Musée"

### Gala Dinner

## Château de Sassenage Tuesday, June 9<sup>th</sup> 2015

The NEWCAS 2015 Gala dinner will take place on Sassenage Castel.

Built in the 17th century by Charles Louis Alphonse de Sassenage, this classic architecture castle is the last of three houses built by the powerful lords of Sassenage. Work of the architect Laurent Valence Summary, reflects the lifestyle of the Grand Century grandeur and magnificence which rhyme with

sweetness and joy of living. The site, consisting of the castle and its landscaped grounds of the  $19^{th}$  century, is classified as a historical monument.

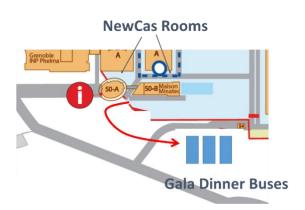

Sassenage Castel is 7km from Minatec so you will have to take buses to join the Gala Dinner. Buses will leave at 18:30 from the parking situated close to Minatec (as indicated in the map below).

A drink will be served in the castel garden. You will then be enjoying the delicious french cuisine. Good music (with the famous group: Nuage de Swing) and excellent french wine will be there for our great party so don't miss it.

### To go to the Gala dinner:

Transportation to the "Château de Sassenage" will be available.

Buses will depart from Minatec at 18:30.

# Technical program

## Sunday, June 7th

### LOCATION: PHELMA Engineering School.

**08:30-10:00** Session 1A: Tutorial 1 - Injection Locked Oscillators: Applications, Modeling, and Design - Part I

LOCATION: Amphitheatre 001

Tony Chan Carusone

University of Toronto

08:30-10:00 Session 1B: Tutorial 2 - FDSOI Technology - Part I - Body Biasing techniques in UTBB

LOCATION: Room 002

Philippe Flatresse

ST Microelectronics

10:00-10:30Coffee Break

10:30-12:00 Session 2A: Tutorial 1 - Injection Locked Oscillators: Applications, Modeling, and Design - Part II

LOCATION: Amphitheatre 001

Tony Chan Carusone

University of Toronto

10:30-12:00 Session 2B: Tutorial 2 - FDSOI Technology - Part II - Millimeter Wave 28nm-CMOS FD SOI Power Amplifier Design

LOCATION: Room 002

Eric Kerhervé, Aurélien Larie, Baudouin Martineau

IMS

12:00-13:30Lunch Break

13:30-15:00 Session 3A: Tutorial 3 - Full Software Radio Circuits and Systems: Design by Mathematics in 28nm FDSOI Technology and Application to 5G Standard - Part I

LOCATION: Amphitheatre 001

Yann Deval, François Rivet, Yoan Veyrac, Nassim Bouassida IMS

13:30-15:00 Session 3B: Tutorial 4 - Substrate Integrated Waveguides: from PCB to Microelectronics Technologies - Part I

LOCATION: Room 002

Ke Wu

Polytechnique Montréal

15:00-15:30Coffee Break

15:30-17:00 Session 4A: Tutorial 3 - Full Software Radio Circuits and Systems: Design by Mathematics in 28nm FDSOI Technology and Application to 5G Standard - Part II

LOCATION: Amphitheatre 001

<u>Yann Deval, François Rivet, Yoan Veyrac, Nassim Bouassida</u> IMS

15:30-17:00 Session 4B: Tutorial 4 - Substrate Integrated Waveguides: from PCB to Microelectronics Technologies - Part II

LOCATION: Room 002

Ke Wu

Polytechnique Montréal

18:00-19:30 Welcome reception - La Bastille

## Monday, June 8th

### LOCATION: Minatec Conference Center

08:30-09:10 Opening Ceremony

LOCATION: Auditorium

09:10-10:10 Session 6: Plenary Lecture J. Sifakis

LOCATION: Auditorium

SESSSION CHAIR: M. Belleville - CEA-LETI

Joseph Sifakis

The Internet of Things - The Ultimate ICT Revolution

**EPFL**

10:10-10:30 Coffee Break

10:30-12:00 Session 7A: Phase Locked Loops and Circuits for Optical Communications

LOCATION: Auditorium

SESSSION CHAIR: R. Lababidi - IM2NP, F. Hameau - CEA-LETI

7A1 <u>Anh Chu, Navneeta Deo, Waqas Ahmad, Markus Törmänen</u> and <u>Henrik Sjöland</u>

An Ultra-low Power Charge-Pump PLL with High Temperature Stability in 130 nm CMOS

Lund University

7A2 Khaldoon Abugharbieh and Karam Gharbieh

A 20 Gbps Voltage Mode Transmitter with a High-Frequency Signal Boost in 28nm CMOS Technology

Princess Sumaya University for Technology

7A3 <u>Konstantinos Moustakas</u> and <u>Stylianos Siskos</u>

Low Voltage CMOS Charge Pump with Excellent Current Matching Based on a Rail-to-Rail Current Conveyor

Aristotle University of Thessaloniki

7A4 Robert Polster<sup>1</sup>, José Luis Gonzalez-Jimenez<sup>1</sup> and Eric Cassan<sup>2</sup>

A Novel Optical Integrate and Dump Receiver for Clocking Signals  $^{1}CEA\ LETI, ^{2}IEF$

7A5 <u>Maciej Kucharski</u>, <u>Frank Herzel</u> and <u>Dietmar Kissinger</u>